#### WE7275 先頭サンプル時刻報告書

- 1 先頭サンプルの時刻(トリガ(t=0)基準)の算出方法 算出方法を導き出すために、トリガ信号(パルス)自身の波形を測定し、トリガの立ち上がり位置を特定 し、その測定結果より、以下の算出方法とした。 測定結果については、第2章以降に記述した。

- 1. 1 サンプリング・クロックに外部クロックを指定した場合 (ソース:デモジュレータ)

サンプリング周期=外部クロック時間である。

- (1) FreeRun モード、Event モード

- (a) 外部クロックの開始が、トリガより-2クロック以前の場合 先頭サンプルの時刻 =  $-1 \times$ サンプリング周期

- (b) 外部クロックの開始が、トリガより-1クロック以降の場合 先頭サンプルの時刻 = 外部クロックの開始時刻+サンプリング周期

- (2) プリサンプルモード

- (a) 外部クロックの開始が、トリガより-(2+プリサンプル数)クロック以前の場合 先頭サンプルの時刻 = -(1+プリサンプル数)×サンプリング周期

- (b) 外部クロックの開始が、トリガよりー(1+プリサンプル数)クロック以降の場合先頭サンプルの時刻 先頭サンプルの時刻 = 不定 第2サンプルの時刻 = 外部クロックの開始時刻+サンプリング周期

- 1. 2 サンプリング・クロックに内部クロックを指定した場合 サンプリングは、どのモードでも、トリガ前に不定タイミングで開始されているので、最大、サンプリング周期のジッタが発生する。

- (1) FreeRun モード、Event モード

先頭サンプルの時刻 =  $tx \times サンプリング周期+ジッタ$ tx = サンプリング周期 1us(1MHz):-1、左記以外:0

(2) プリサンプルモード

先頭サンプルの時刻 = -(プリサンプル数)×サンプリング周期+ジッタ

### 2 外部クロック使用時、測定資料

### 2. 1 測定内容

- ・外部クロックは FPGA デモジュレータを使用した。

- ・入力パルス (トリガ) は外部クロックの立ち上げりから 20ns~30ns 程度前である。(オシロ観測)

- ・外部クロックの開始タイミングを、トリガ位置からずらしながら、入力パルスの波形を測定した。

- ・外部クロックレート(サンプルレート)は、1MHz, 100kHz, 10kHz とした。

- ・測定モードは、FreeRun モード, Event モード, プリサンプルモード (PreSample:10) とした。

### 2. 2 測定結果

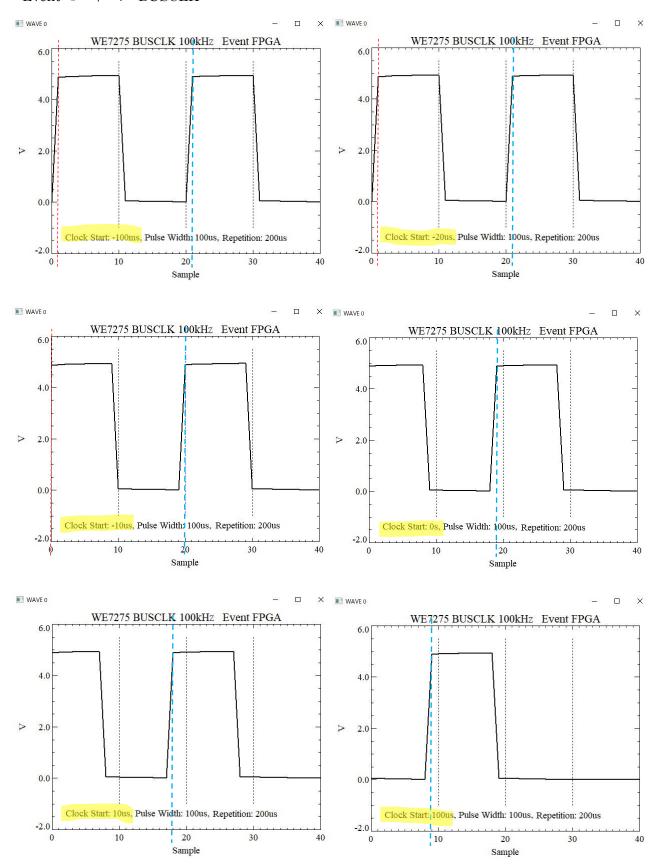

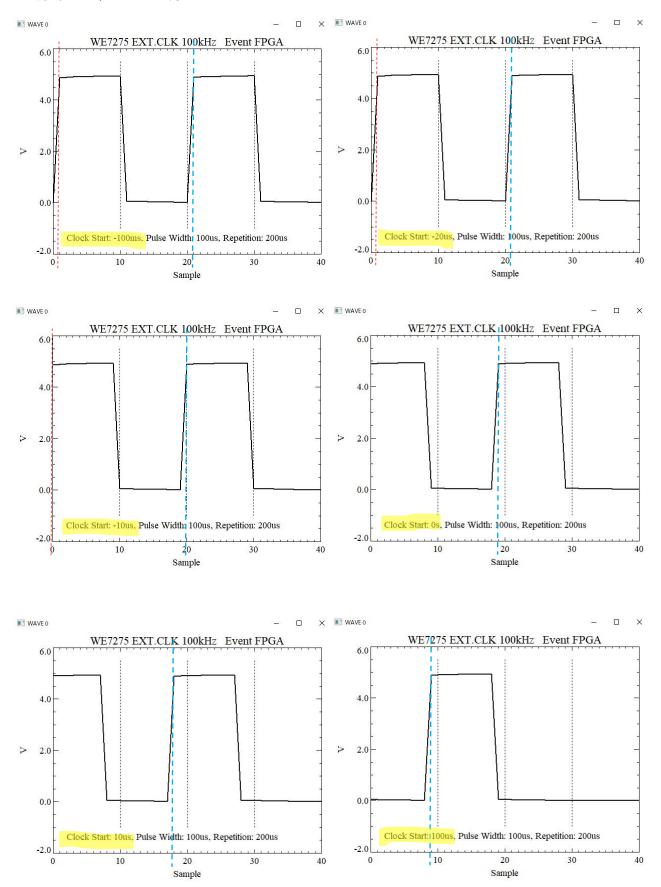

- ・FreeRun モードと Event モードでは、結果が同じになった。

- ・全サンプルレートにおいて、同等の結果になった。

| Comple         | ClockStart   | 先頭サンプル from trigger (Clock) |         |        |         |

|----------------|--------------|-----------------------------|---------|--------|---------|

| Sample<br>Rate | from trigger | FreeRun                     |         | Event  |         |

|                | (Clock)      | BUSCLK                      | EXT.CLK | BUSCLK | EXT.CLK |

|                | -100000      | -1                          | -1      | -1     | -1      |

|                | -2           | -1                          | -1      | -1     | -1      |

|                | -1           | 0                           | 0       | 0      | 0       |

|                | 0            | 1                           | 1       | 1      | 1       |

|                | 1            | 2                           | 2       | 2      | 2       |

|                | 10           | 11                          | 11      | 11     | 11      |

| 1MHz           |              | PreSample:10                |         |        |         |

|                |              | BUSCLK                      | EXT.CLK |        |         |

|                | -100000      | -11                         | -11     |        |         |

|                | -12          | -11                         | -11     |        |         |

|                | -11          | -11                         | -11     |        |         |

|                | -10          | -10                         | -10     |        |         |

|                | -8           | -8                          | -8      |        |         |

|                | -6           | -6                          | -6      |        |         |

|                | -2           | -2                          | -2      |        |         |

|                | -1           | -1                          | -1      |        |         |

|                | 0            | 0                           | 0       |        |         |

|                | 1            | 1                           | 1       |        |         |

|                | 10           | 10                          | 10      |        |         |

| Comple         | ClockStart   | 先頭サンプル from trigger (Clock) |         |        |         |

|----------------|--------------|-----------------------------|---------|--------|---------|

| Sample<br>Rate | from trigger | FreeRun                     |         | Event  |         |

|                | (Clock)      | BUSCLK                      | EXT.CLK | BUSCLK | EXT.CLK |

|                | -10000       | -1                          | -1      | -1     | -1      |

|                | -2           | -1                          | -1      | -1     | -1      |

|                | -1           | 0                           | 0       | 0      | 0       |

|                | 0            | 1                           | 1       | 1      | 1       |

| 100kHz         | 1            | 2                           | 2       | 2      | 2       |

|                | 10           | 11                          | 11      | 11     | 11      |

|                |              | PreSample:10                |         |        |         |

|                |              | BUSCLK                      | EXT.CLK |        |         |

|                | -10000       | -11                         | -11     |        |         |

|                | -12          | -11                         | -11     |        |         |

|                | -11          | -11                         | -11     |        |         |

|                | -10          | -10                         | -10     |        |         |

|                | -8           | -8                          | -8      |        |         |

|                | -6           | -6                          | -6      |        |         |

|                | -2           | -2                          | -2      |        |         |

|                | -1           | -1                          | -1      |        |         |

|                | 0            | 0                           | 0       |        |         |

|                | 1            | 1                           | 1       |        |         |

|                | 10           | 10                          | 10      |        |         |

| Camanla        | ClockStart   | 先頭サンプル from trigger (Clock) |         |        |         |

|----------------|--------------|-----------------------------|---------|--------|---------|

| Sample<br>Rate | from trigger | FreeRun                     |         | Event  |         |

|                | (Clock)      | BUSCLK                      | EXT.CLK | BUSCLK | EXT.CLK |

| 10kHz          | -1000        | -1                          |         | -1     |         |

|                | -2           | -1                          |         | -1     |         |

|                | -1           | 0                           |         | 0      |         |

|                | 0            | 1                           |         | 0      |         |

|                | 1            | 2                           |         | 2      |         |

|                | 7            | 8                           |         | 8      |         |

|                |              | PreSample:10                |         |        |         |

|                |              | BUSCLK                      | EXT.CLK |        |         |

|                | -1000        | -11                         |         |        |         |

|                | -12          | -11                         |         |        |         |

|                | -11          | -11                         |         |        |         |

|                | -10          | -10                         |         |        |         |

|                | -8           | -8                          |         |        |         |

|                | -6           | -6                          |         |        |         |

|                | -2           | -2                          |         |        |         |

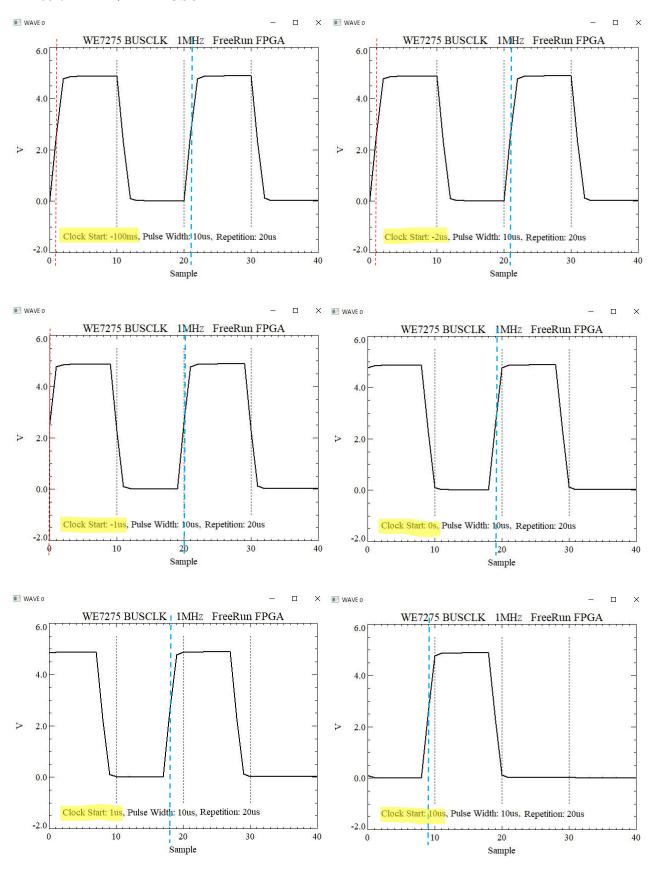

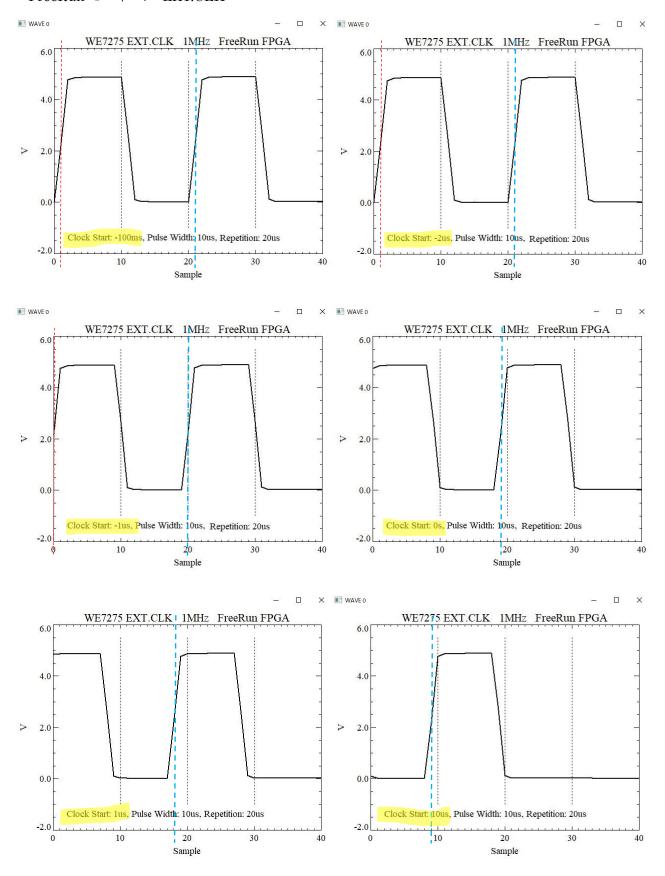

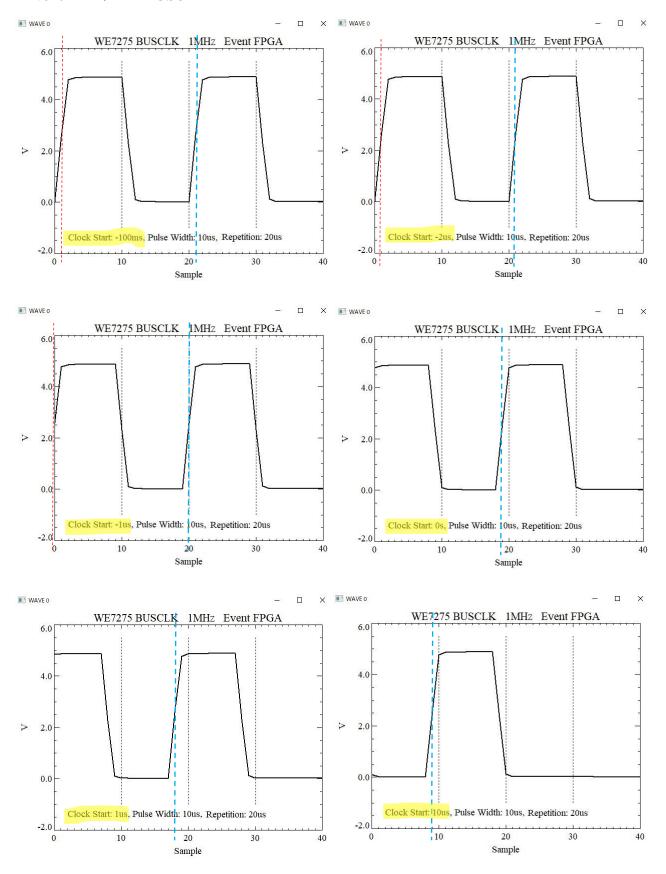

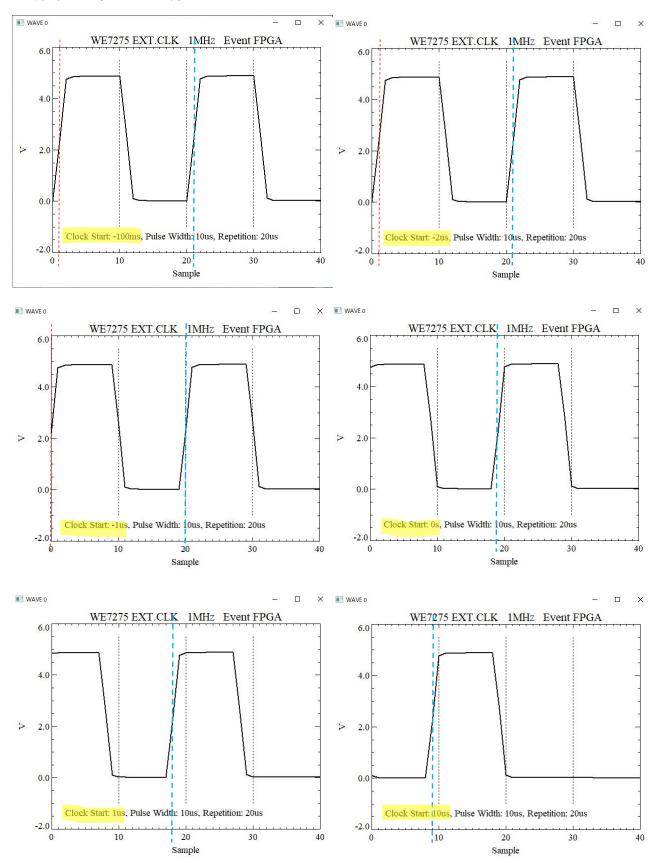

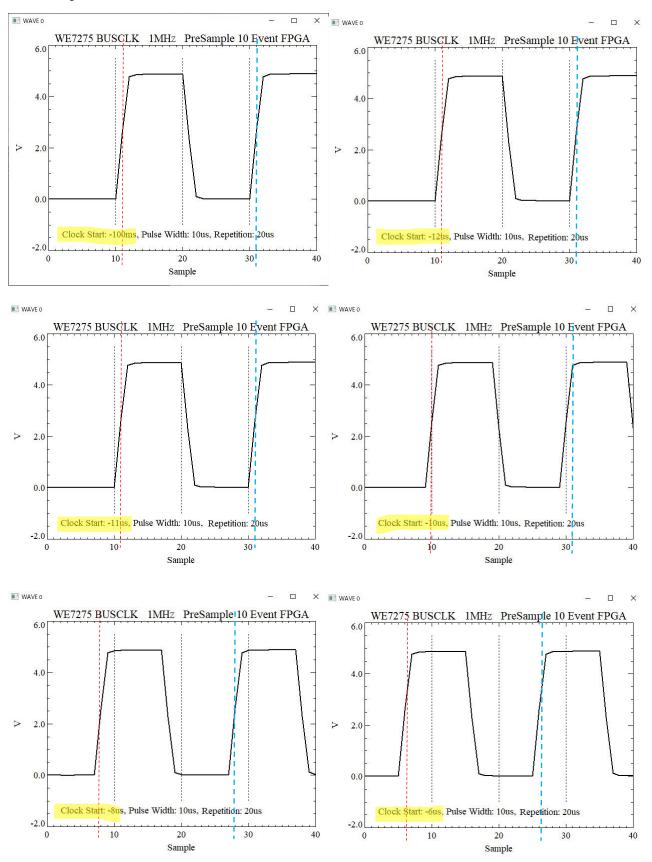

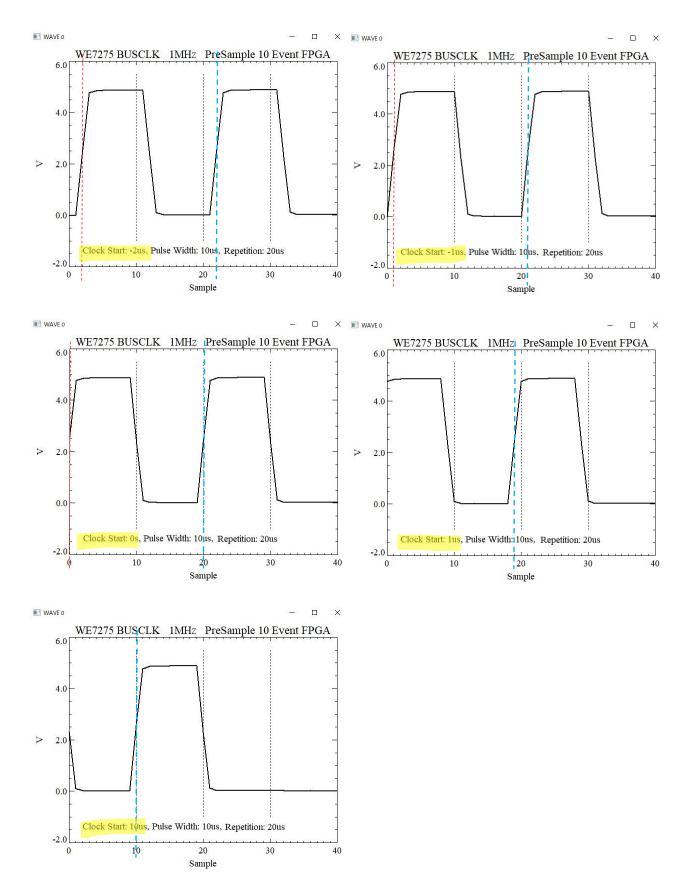

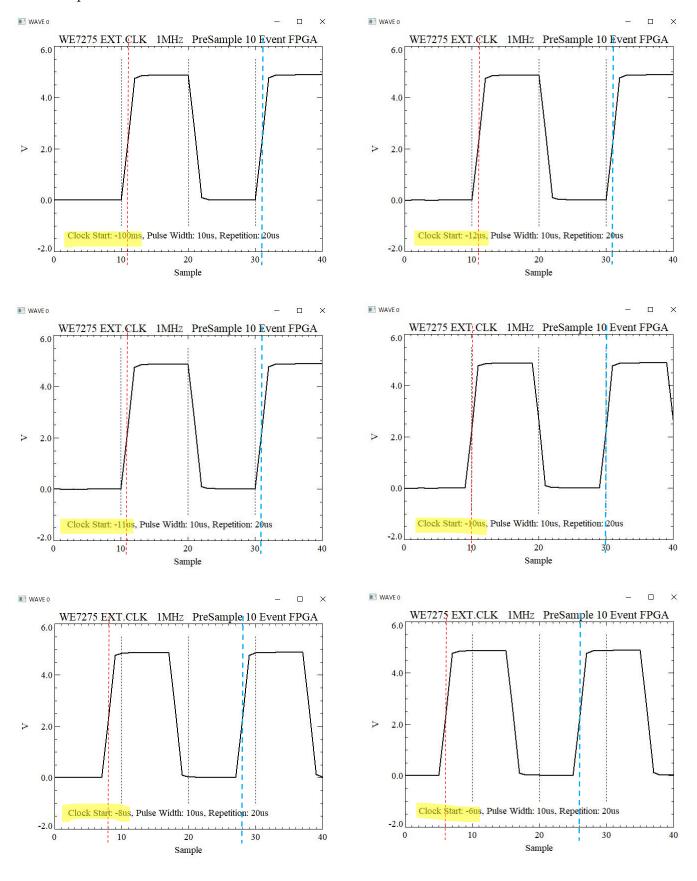

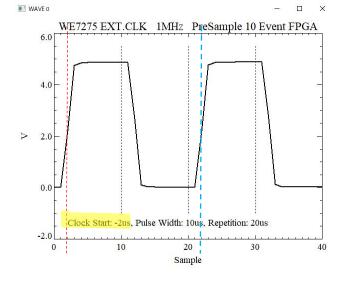

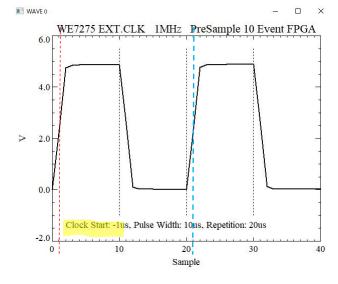

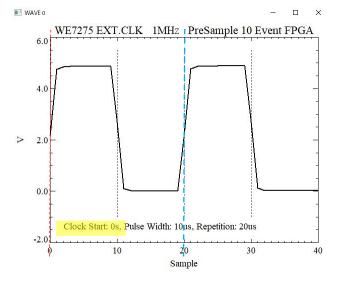

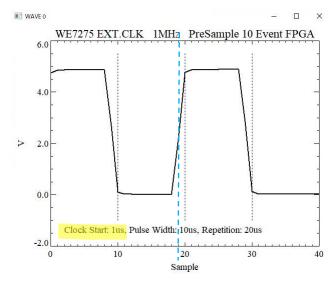

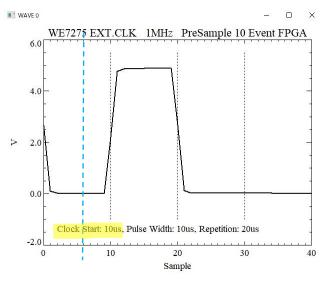

### 2. 3 測定結果グラフ

赤点線:トリガの立ち上がり 水色点線:2回めパルスの立ち上がり

# (1) 1MS/s

トリガタイミングから 10us 幅パルスを 20us 繰り返しで 2 発入力した。

# ・FreeRun モード / BUSCLK

# ・FreeRun モード / EXT.CLK

# ・Event モード / BUSCLK

# ・Event モード / EXT.CLK

### • PreSample=10 / BUSCLK

### • PreSample=10 / EXT.CLK

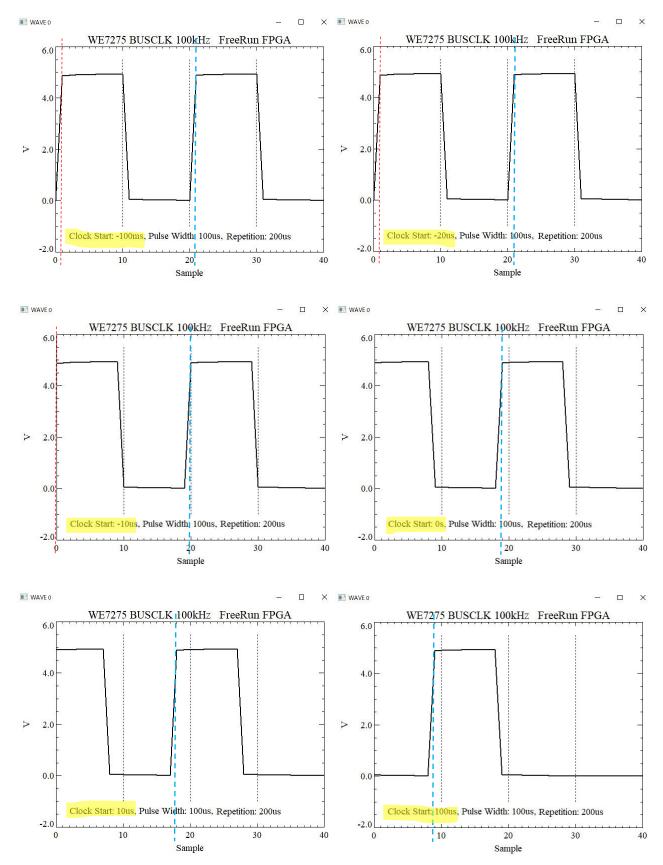

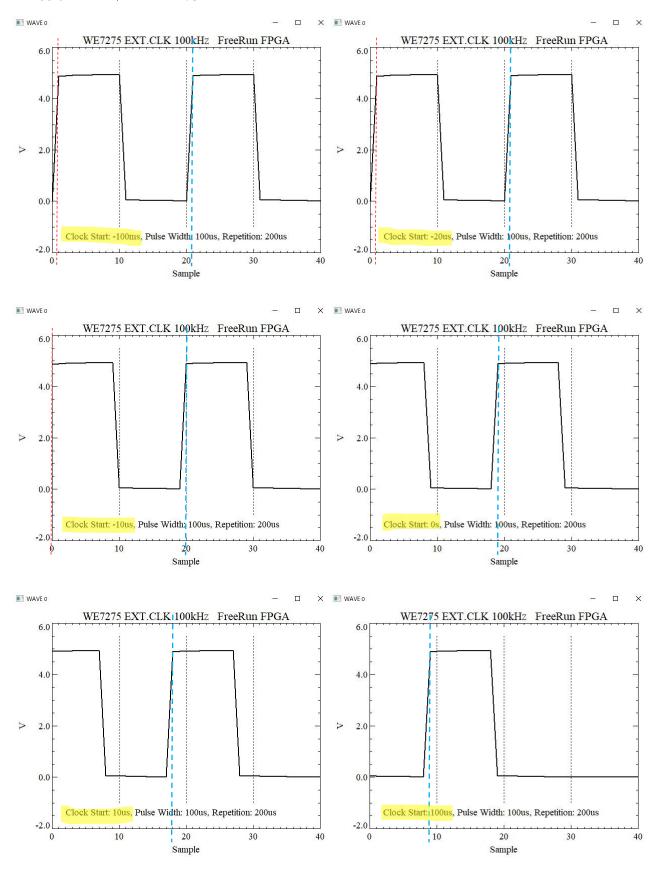

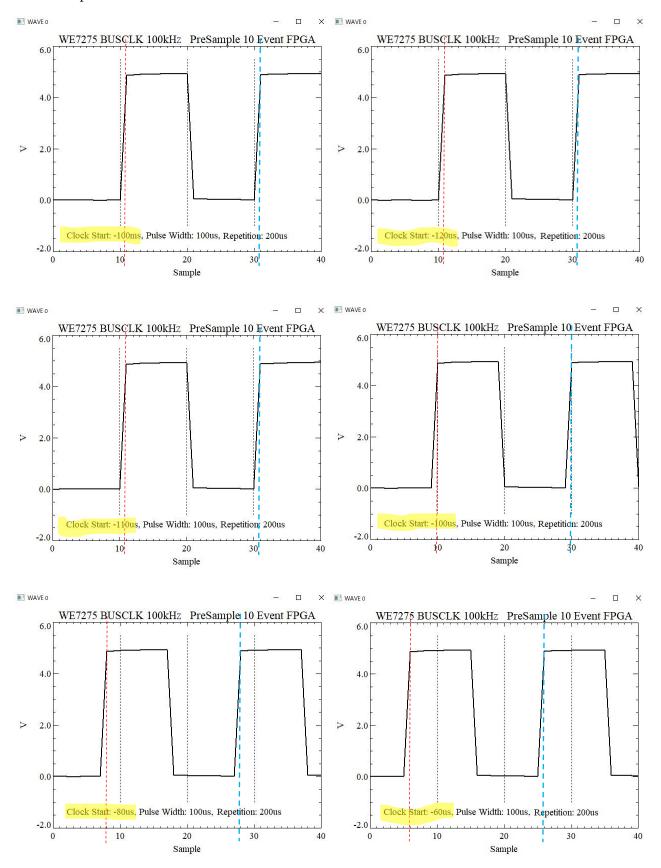

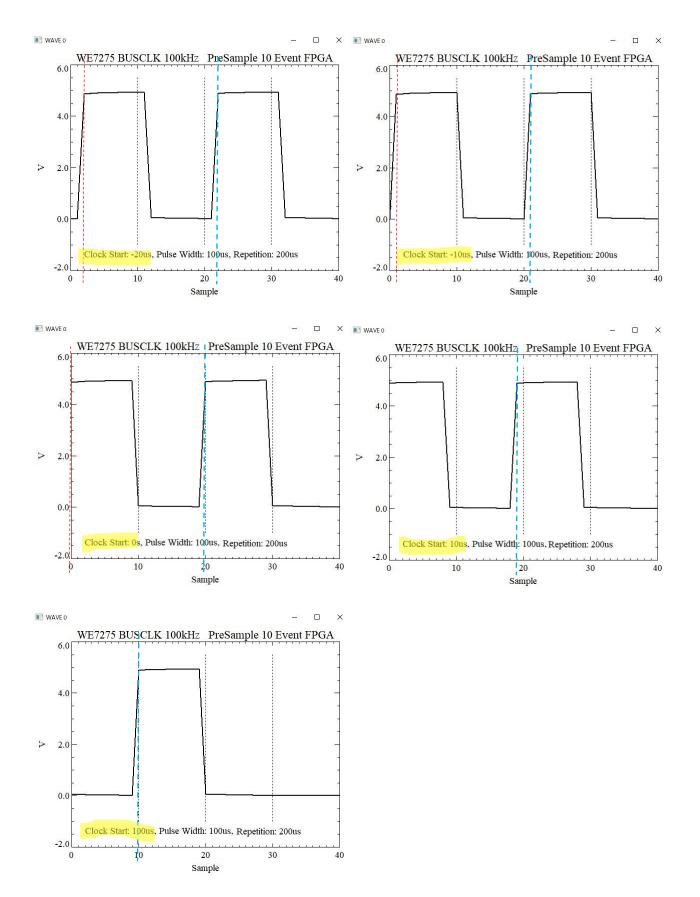

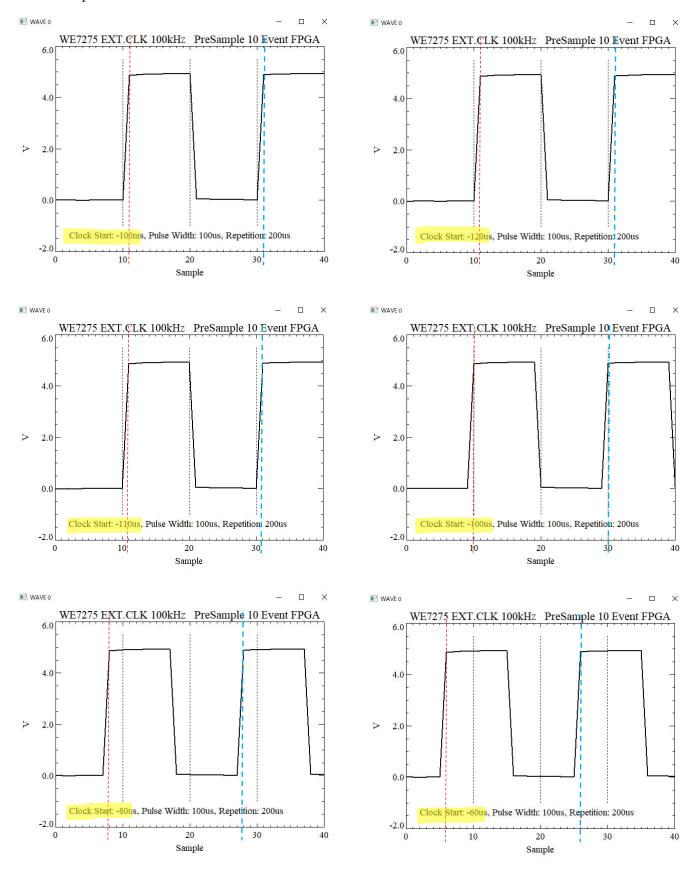

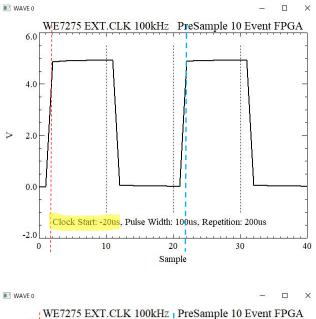

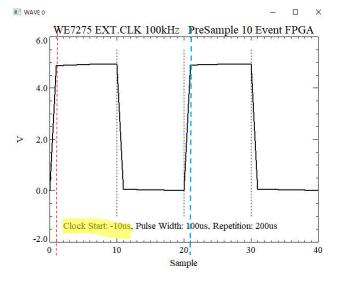

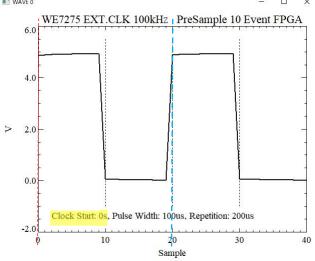

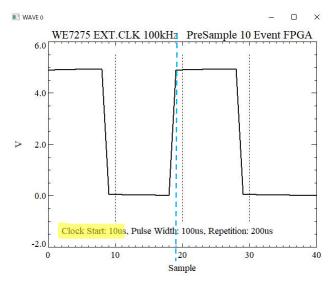

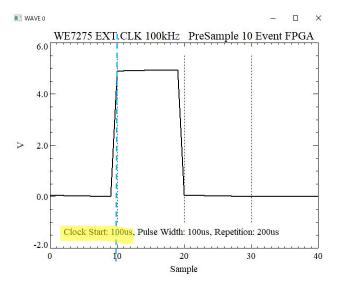

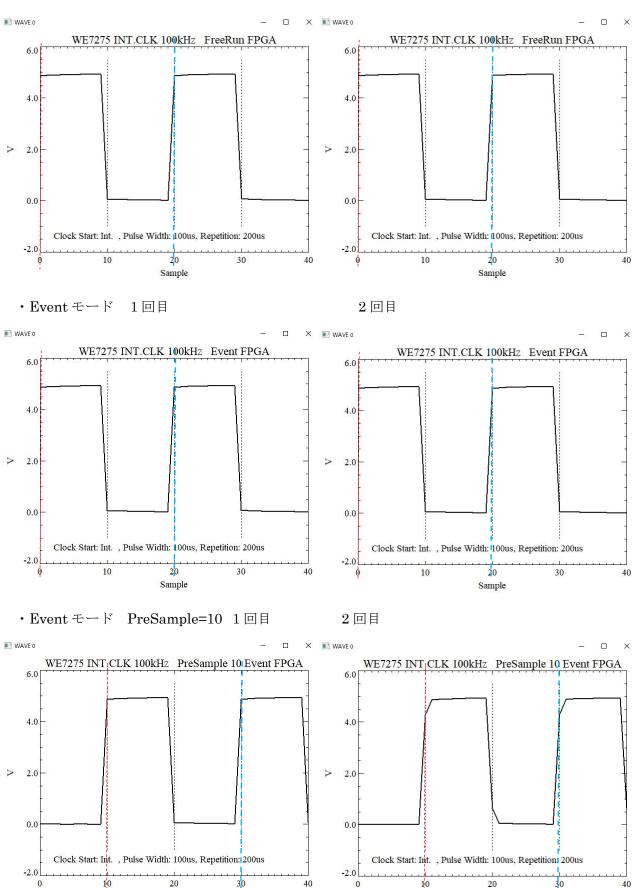

### (2) 100kS/s

トリガタイミングから 100us 幅パルスを 200us 繰り返しで 2 発入力した。

#### ・FreeRun モード / BUSCLK

### ・FreeRun モード / EXT.CLK

# ・Event モード / BUSCLK

### ・Event モード / EXT.CLK

### · PreSample=10 / BUSCLK

### • PreSample=10 / EXT.CLK

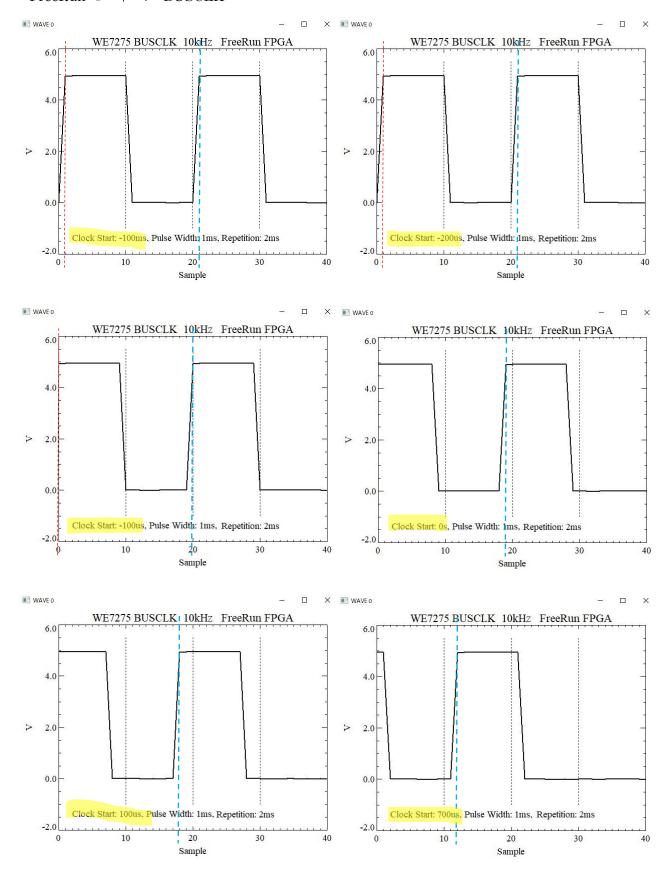

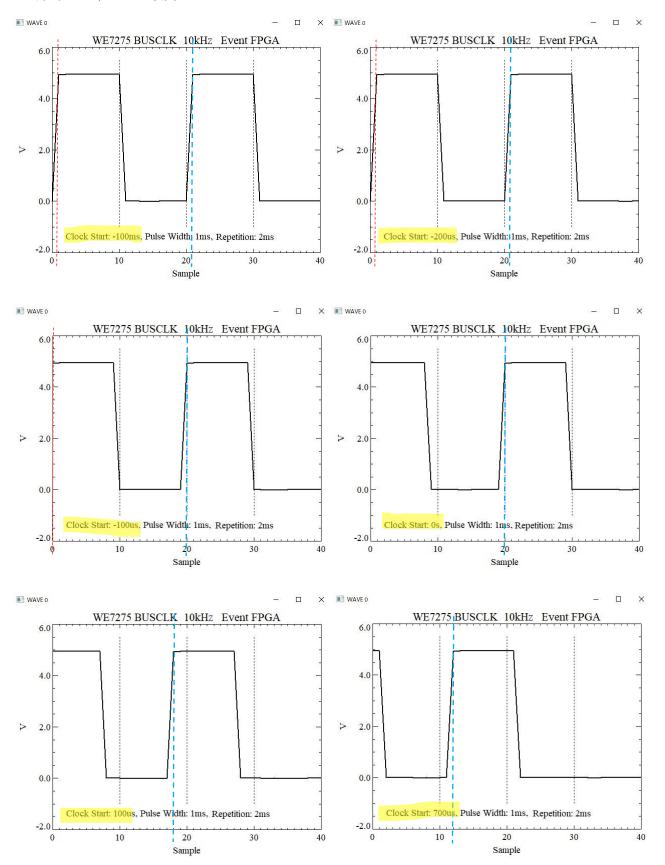

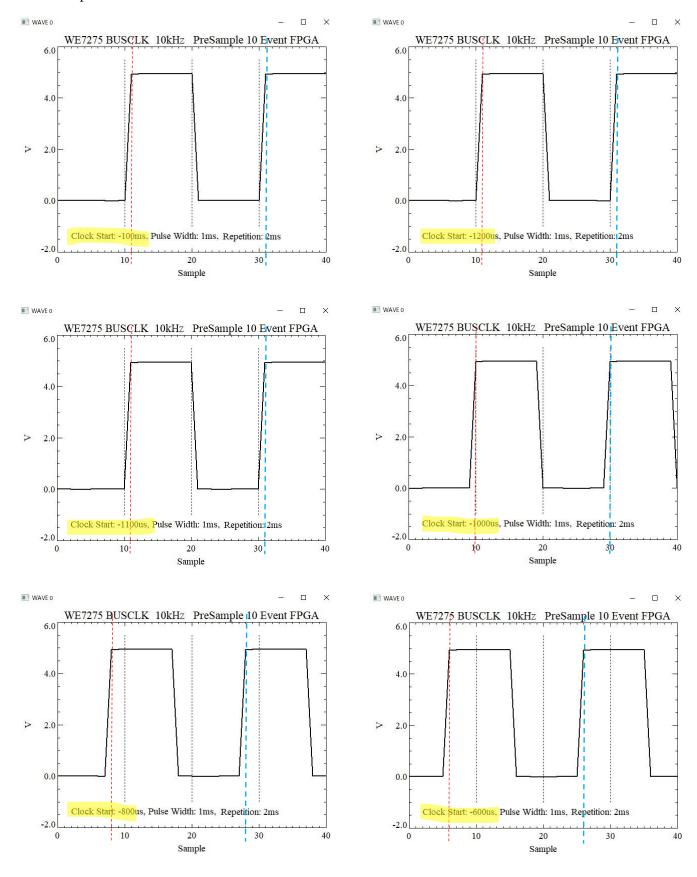

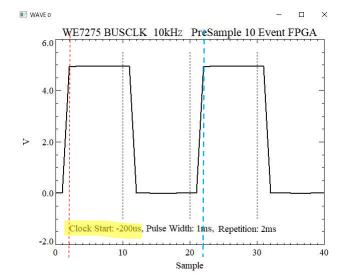

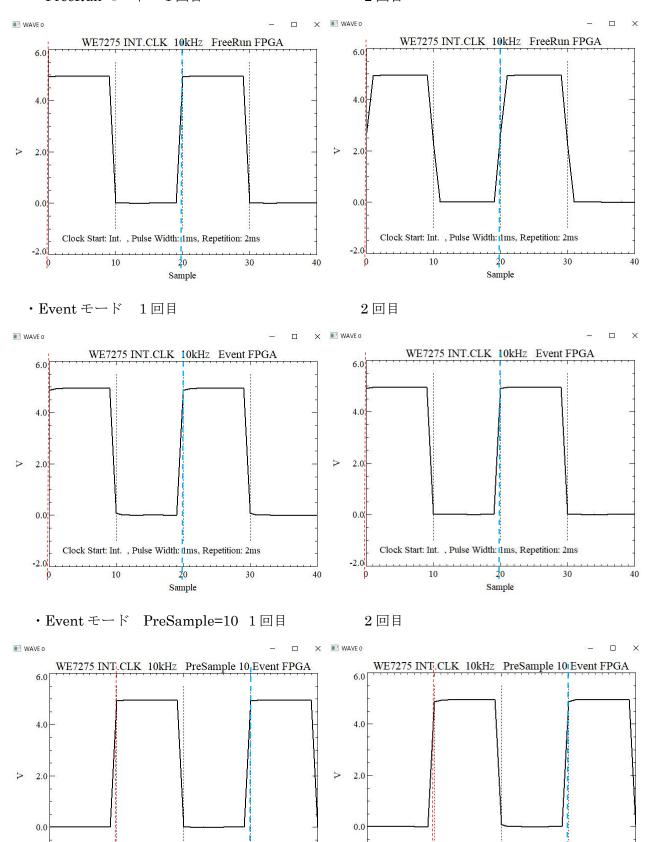

#### (3) 10kS/s

トリガタイミングから 1ms 幅パルスを 2ms 繰り返しで 2 発入力した。

### ・FreeRun モード / BUSCLK

# ・Event モード / BUSCLK

### • PreSamples=10 / BUSCLK

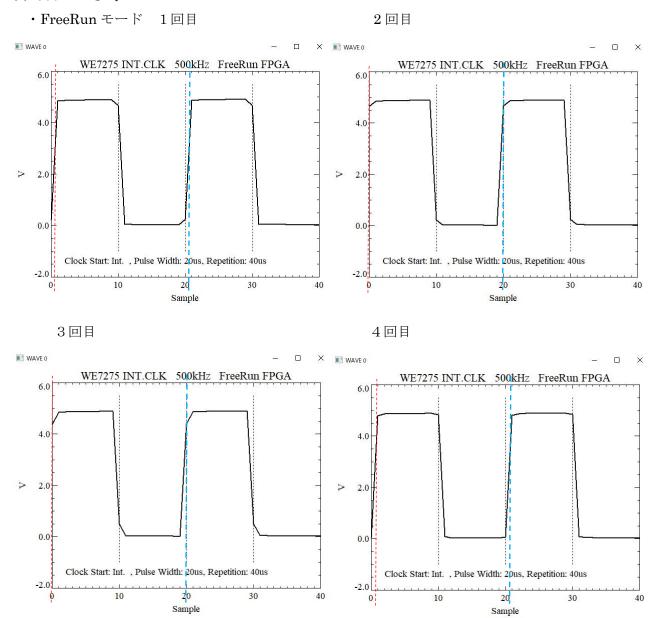

### 3 内部クロック

# 3. 1 測定内容

- ・サンプルレートは、1MHz, 100kHz, 10kHz とした。(500kHz)

- ・測定モードは、FreeRun モード, Event モード, プリサンプルモード (PreSample:10) とした。

### 3. 2 測定結果

| Sample | 先頭サンプル from trigger (clocks) |       |              |  |

|--------|------------------------------|-------|--------------|--|

| Rate   | FreeRun                      | Event | PreSample:10 |  |

| 1MHz   | -1                           | -1    | -10          |  |

| 100kHz | 0                            | 0     | -10          |  |

| 10kHz  | 0                            | 0     | -10          |  |

# 3. 3 測定結果グラフ

赤点線:トリガの立ち上がり 水色点線:2回めパルスの立ち上がり

#### (1) 1MHz

・FreeRun モード 1回目 2回目 - □ × ■ WAVE 0 WAVE 0 WE7275 INT.CLK 1MHz FreeRun FPGA WE7275 INT.CLK 1MHz FreeRun FPGA 2.0 2.0 0.0 Clock Start: Int. , Pulse Width: 10us, Repetition: 20us Clock Start: Int., Pulse Width: 10us, Repetition: 20us 10 20 30 10 20 40 ・Event モード 1回目 2回目 − □ X ■ WAVE 0 WAVE 0 WE7275 INT.CLK 1MHz Event FPGA WE7275 INT.CLK 1MHz Event FPGA 60 4.0 4.0 2.0 0.0 Clock Start: Int. , Pulse Width: 10us, Repetition: 20us Clock Start: Int. , Pulse Width: 10us, Repetition: 20us 20 20 10 0 10 Sample ・Event モード PreSample=10 1回目 2回目 WAVE 0 - □ X ■ WAVE 0 WE7275 INT.CLK 1MHz PreSample 10 Event FPGA WE7275 INT.CLK 1MHz PreSample 10 Event FPGA 4.0 4.0 Clock Start: Int., Pulse Width: 10us, Repetition: 20us Clock Start: Int. , Pulse Width: 10us, Repetition: 20us

Sample

40

20

Sample

# (2) 100kHz

・FreeRun モード 1回目 2回目

Sample

Sample

#### (3) 10kHz

・FreeRun モード 1回目

2回目

40

Clock Start: Int., Pulse Width: 1ms, Repetition: 2ms

Sample

Clock Start: Int. , Pulse Width: 1ms, Repetition: 2ms

Sample

## (4) 500kHz 参考

以上